Budowa urządzenia

Rejestrator zbudowany jest z modułu głównego, odpowiedzialnego za obróbkę dźwięku i komunikację z komputerem oraz z interfejsów linii telefonicznych, których liczba może być dowolna, jednak nie przekraczająca 16. Jedna płytka interfejsu obsługuje dwie linie, więc maksymalna liczba linii obsługiwanych przez urządzenie wynosi 32.

Moduł główny

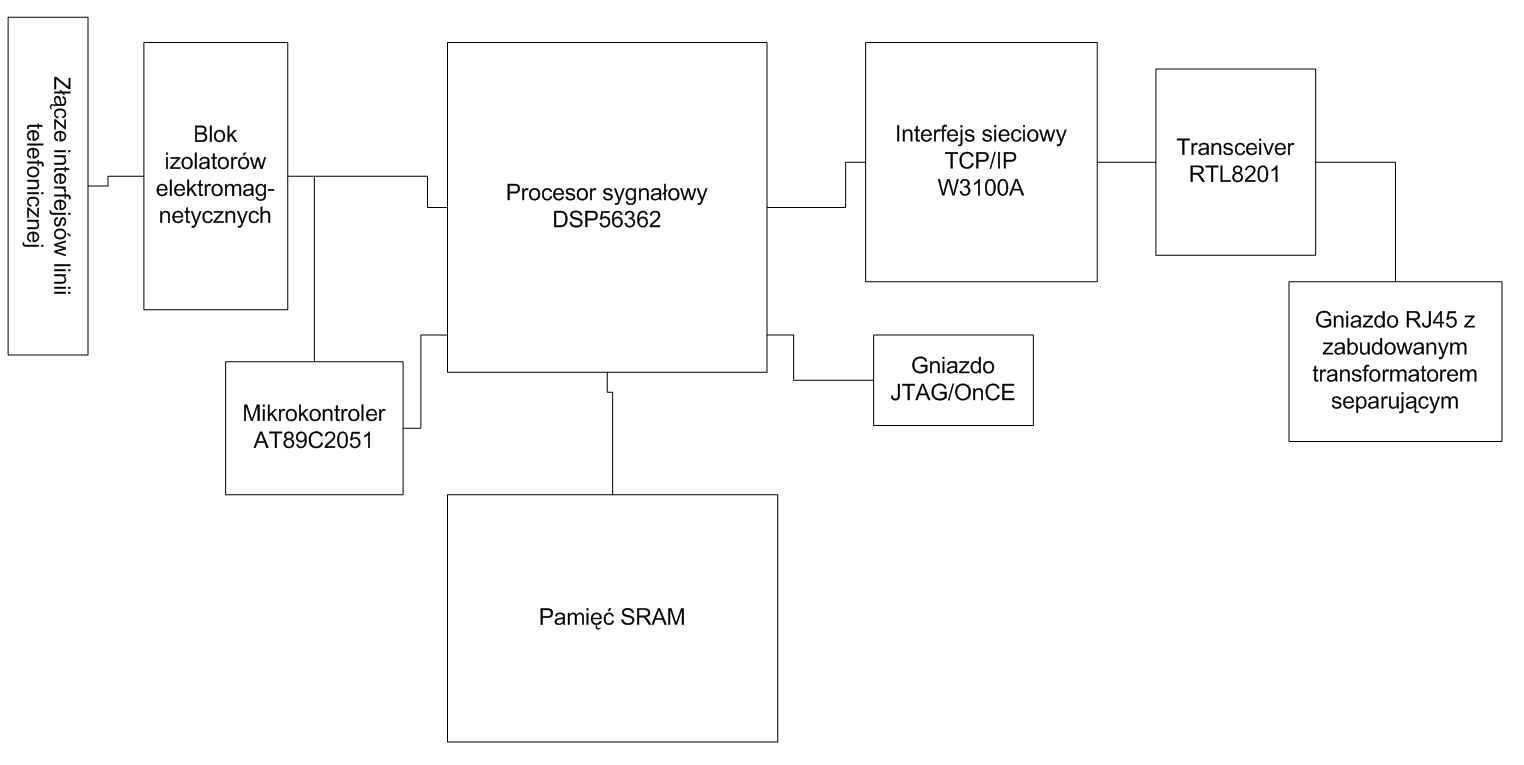

Moduł główny, którego struktura widoczna jest na rysunku 4.1, zbudowany jest z następujących elementów:

procesor sygnałowy Motorola DSP56362,

pamięć SRAM 256 kilosłów 16-bitowych,

układ realizujący stos TCP/IP WIZnet W3100A,

interfejs warstwy fizycznej Ethernetu Realtek RTL8201BL,

mikrokontroler Atmel AT89C2051.

Rys. 4.1. Schemat blokowy modułu głównego rejestratora

Schemat ideowy modułu głównego zamieszczony jest w dodatku A. Jądro modułu stanowi procesor DSP. Przechwytuje on dane głosowe pochodzące od płytek interfejsów linii telefonicznych i buforuje je w pamięci SRAM. Poza tym odbiera dane sterujące z mikrokontrolera AT89C2051, na podstawie których komputer będzie podejmował odpowiednie działania, jak na przykład rozpoczęcie lub zakończenie rejestracji. Kolejnym zadaniem procesora DSP jest automatyczna regulacja wzmocnienia, o ile użytkownik włączy tę funkcję. Ponadto DSP steruje wymianą danych z komputerem przez układ W3100A.

Układ W3100A organizuje nadawane dane w pakiety TCP/IP oraz dekoduje przychodzące pakiety. Układ ten współpracuje z transceiverem RTL8201, który zapewnia konwersję pomiędzy poziomami logicznymi standardu CMOS i sygnałami zgodnymi ze standardem Ethernet oraz odpowiada za wykrywanie kolizji. Sygnały z transceivera wyprowadzone są na gniazdo RJ45 przez transformator separujący, zabudowany we wspólnej obudowie z gniazdem.

Mikrokontroler Atmel pełni dwie funkcje. Po pierwsze, po uruchomieniu urządzenia ładuje do mikroprocesora DSP56362 program startowy, którego zadaniem jest załadowanie właściwego programu z komputera przez łącze Ethernet. Po drugie, w trakcie normalnej pracy rejestratora mikrokontroler AT89C2051 odbiera szeregowo dane sterujące z płytek interfejsów linii i przesyła je do procesora DSP. W obydwu przypadkach komunikacja mikrokontrolera z procesorem DSP odbywa się przy użyciu protokołu szeregowego SPI.

W celu ułatwienia testowania płytka została wyposażona w złącze połączone z portem OnCE/JTAG procesora sygnałowego. Zapewnia to możliwość pracy krokowej oraz obserwacji i zmiany zawartości rejestrów mikroprocesora w trakcie działania programu.

Interfejs linii telefonicznej

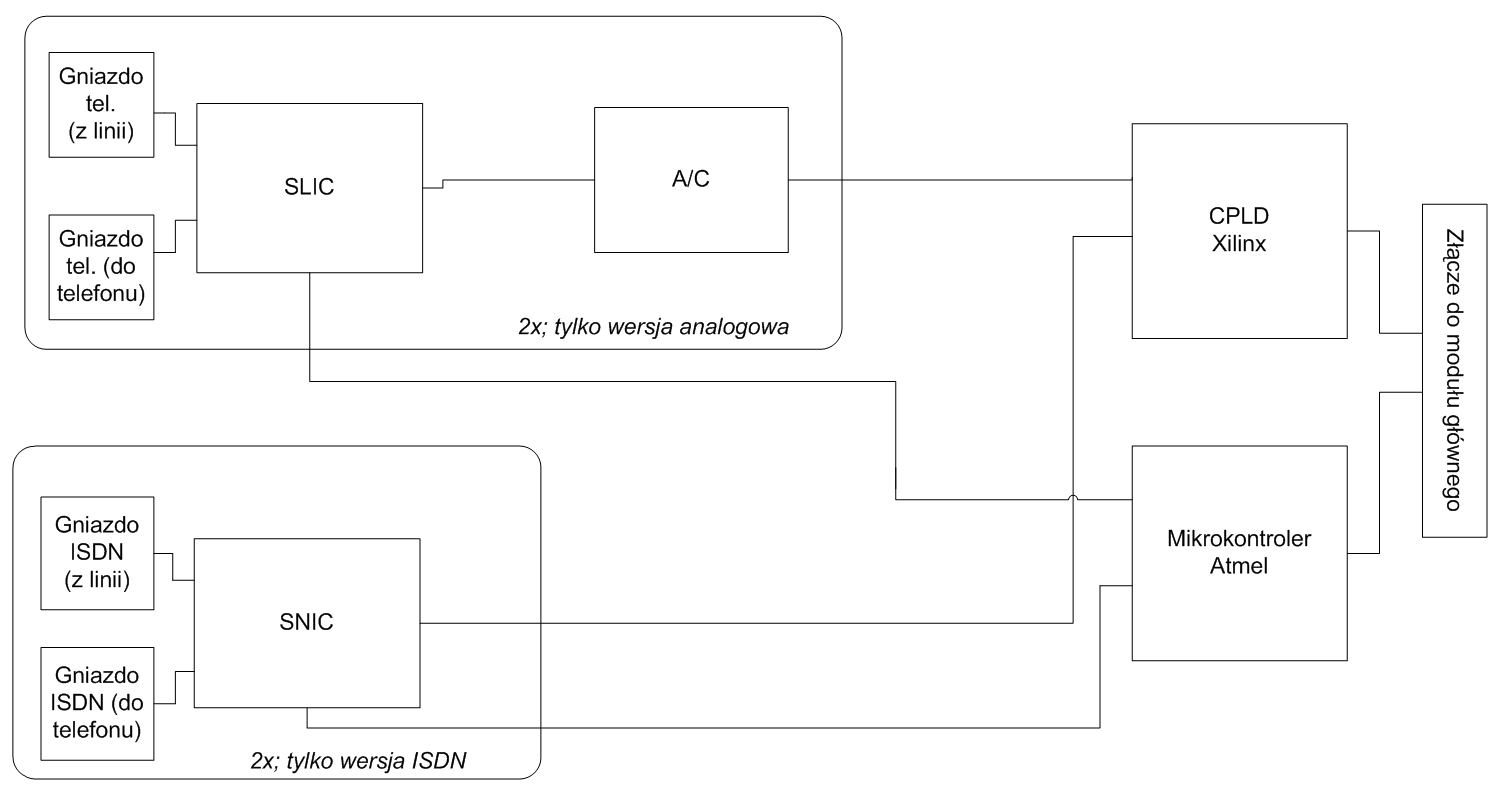

Zadaniem interfejsu linii jest wykrywanie zdarzeń takich jak rozpoczęcie i zakończenie rozmowy oraz pobieranie próbek głosu. W przypadku linii analogowej konieczne jest przekształcenie sygnału analogowego na próbki cyfrowe. Struktura modułu interfejsu linii została przedstawiona na rysunku 4.2.

Jeden moduł obsługuje dwie linie telefoniczne. Moduł ten może być wykonany w wersji obsługującej linie analogowe lub cyfrowe (ISDN) lub też w wersji mieszanej obsługującej po jednej linii każdego rodzaju. Występują tu elementy wspólne dla każdej z wersji – układ CPLD firmy Xilinx i mikrokontroler Atmel oraz elementy zależne od typu obsługiwanej linii. Dla linii analogowej są to:

dwa gniazda telefoniczne, umożliwiające podłączenie urządzenia do linii telefonicznej oraz do aparatu telefonicznego,

układ SLIC (ang. Subscriber Line Interface Circuit),

przetwornik analogowo-cyfrowy.

Rys. 4.2. Schemat blokowy modułu interfejsu linii telefonicznej

Komponentami charakterystycznymi dla linii cyfrowej są:

2 gniazda – analogicznie jak w przypadku linii analogowej,

układ SNIC (ang. Subscriber Network Interface Circuit).

Zadaniem interfejsu SLIC jest przetwarzanie sygnałów prądowych występujących w linii telefonicznej na sygnały napięciowe, które można podać na przetwornik analogowo-cyfrowy. Dodatkowo interfejs ten wykrywa stan linii, tzn. rozpoznaje czy jest prowadzona rozmowa, co pozwala na podjęcie decyzji o rozpoczęciu i zakończeniu rejestracji.

Układ SNIC jest interfejsem linii cyfrowej ISDN. Pozwala on zaadaptować sygnały z linii do postaci łatwej do przetwarzania przez mikroprocesor.

Mikrokontroler Atmel ma za zadanie odbieranie sygnałów o stanie linii od interfejsów SLIC lub SNIC. Na tej podstawie mikrokontroler przesyła informacje o rozpoczęciu i zakończeniu rozmowy do modułu głównego za pomocą asynchronicznego interfejsu szeregowego.

Funkcją układu CPLD jest formatowanie danych głosowych. W przypadku interfejsu linii analogowej układ ten zbiera dane z przetwornika analogowo-cyfrowego i kompresuje je logarytmicznie metodą A-law, po czym wysyła je w odpowiedniej szczelinie czasowej za pomocą synchronicznego interfejsu szeregowego do modułu głównego. W wersji cyfrowej zadanie tego układu jest bardziej skomplikowane. Interfejs SNIC wprawdzie dostarcza danych cyfrowych już w formacie A-law, ale muszą być one zdekodowane przez układ CPLD, aby zsumować sygnały z dwóch kierunków transmisji głosu. Następnie zostają one ponownie zakodowane do formatu A-law i przesłane przez synchroniczny interfejs szeregowy do modułu głównego. Zadanie układu CPLD jest w tym przypadku dodatkowo skomplikowane przez fakt, że dane z linii ISDN taktowane są zegarem niezależnym od zegara interfejsu szeregowego używanego do komunikacji z modułem głównym.

komentarze

Copyright © 2008-2010 EPrace oraz autorzy prac.