Architektura mikroprocesora DSP56362

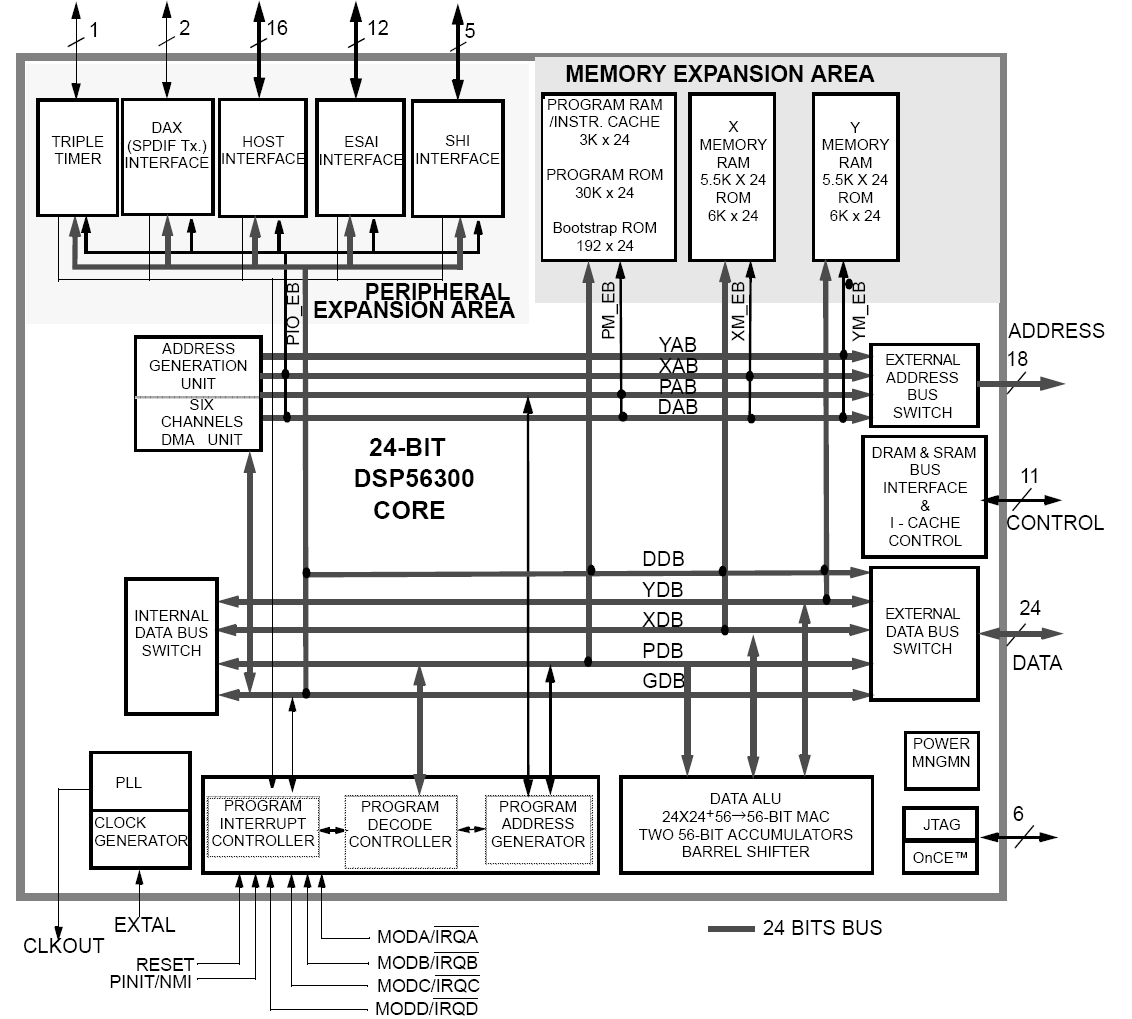

Procesor DSP56362 firmy Motorola należy do rodziny DSP56300. Jego schemat blokowy przedstawiony jest na rysunku 5.1, zaczerpniętym z [2]. Jest to procesor 24-bitowy i operuje na 24-bitowych słowach. Adresowanie jest również 24-bitowe. W jego strukturze można wyodrębnić następujące bloki:

kontroler programu, odpowiedzialny za obsługę potoku, sterowanie biegiem programu (instrukcje skoków, pętli itp.) i obsługę wyjątków,

jednostka arytmetyczno-logiczna (ALU) – wykonująca działania arytmetyczne i operacje logiczne na danych zawartych w rejestrach,

Rys. 5.1. Schemat blokowy procesora DSP56362

trzy bloki wewnętrznej pamięci wraz z oddzielnymi magistralami wewnętrznymi dla każdego z nich,układ generowania adresu (AGU), odpowiedzialny za obsługę licznych trybów adresowania,

układ DMA, umożliwiający przesyłanie danych bez obciążania jednostki centralnej,

port rozszerzenia pamięci, składający się z zewnętrznych magistral danych, adresu i sterującej,

interfejs równoległy Host Port, umożliwiający komunikację z innym mikroprocesorem,

synchroniczny interfejs szeregowy ESAI,

synchroniczny interfejs szeregowy SHI,

synchroniczny interfejs szeregowy DAX,

blok trzech czasomierzy,

interfejs JTAG/OnCE, przeznaczony do celów diagnostycznych,

układ zarządzania energią.

Ważniejsze z powyższych bloków funkcjonalnych zostaną omówione w kolejnych podrozdziałach. Jeżeli nie zachodzi potrzeba użycia któregoś z bloków wykorzystujących wyprowadzenia procesora, mogą być one skonfigurowane jako uniwersalne końcówki we/wy, które użytkownik może wykorzystać w dowolny sposób.

Kontroler programu

Kontroler programu steruje licznikiem programu (PC), decydując w ten sposób o kolejności wykonywania instrukcji, a także czuwa nad kolejnością wykonywania operacji w obrębie jednej instrukcji. Został tu zaimplementowany 7-stopniowy potok, dzięki czemu możliwe jest wykonywania skomplikowanych rozkazów z efektywną szybkością jednego rozkazu na cykl zegara. W celu dalszego zwiększenia szybkości wprowadzono możliwość przesyłania danych równolegle z wykonywaniem operacji arytmetycznych lub logicznych. Aby było to możliwe, zastosowano podział pamięci na trzy bloki P, X, Y oraz wyposażono procesor w trzy oddzielne magistrale do ich obsługi, co zostało dokładniej opisane w podrozdziale 5.2.3.

Po wykonaniu zwykłego rozkazu licznik PC jest inkrementowany o 1. Jednak istnieją rozkazy sterujące biegiem programu, które decydują o innej zmianie licznika PC. Oprócz typowych dla wszystkich procesorów instrukcji skoków warunkowych i bezwarunkowych, wywołań i powrotów, występują tu rozkazy pętli sprzętowych DO i REP. Dzięki nim pętla wykonuje się bez nakładu czasu na skok z końca pętli na jej początek. Rozkazy te korzystają ze specjalnych rejestrów LA i LC.

Oprócz w/w rozkazów, zmiana biegu programu może nastąpić w wyniku wystąpienia przerwania. Procesory rodziny DSP56300 oferują dwa tryby obsługi przerwań:

szybki – procedura obsługi przerwania zajmuje tylko 2 słowa w pamięci programu. Powrót z przerwania następuje automatycznie, bez rozkazu powrotu,

wolny – typowy dla większości innych mikroprocesorów – nie ma ograniczenia na długość procedury obsługującej, ale musi się ona kończyć rozkazem powrotu z przerwania RTI.

Adresy początkowe procedur obsługi przerwań są tworzone w ten sposób, że bity 23..8 są pobierane ze rejestru bazowego VBA, ustawianego przez użytkownika, a bity 7..0 mają wartość zależną od źródła obsługiwanego przerwania.

Na szczególną uwagę zasługuje mechanizm warunkowego wykonywania instrukcji. Programista ma możliwość po niektórych rozkazach wstawić słowo kluczowe IF i podać warunek. Rozkaz opatrzony taką klauzulą będzie wykonany jeżeli warunek jest spełniony, a w przeciwnym wypadku zostanie pominięty.

Jednostka arytmetyczno-logiczna

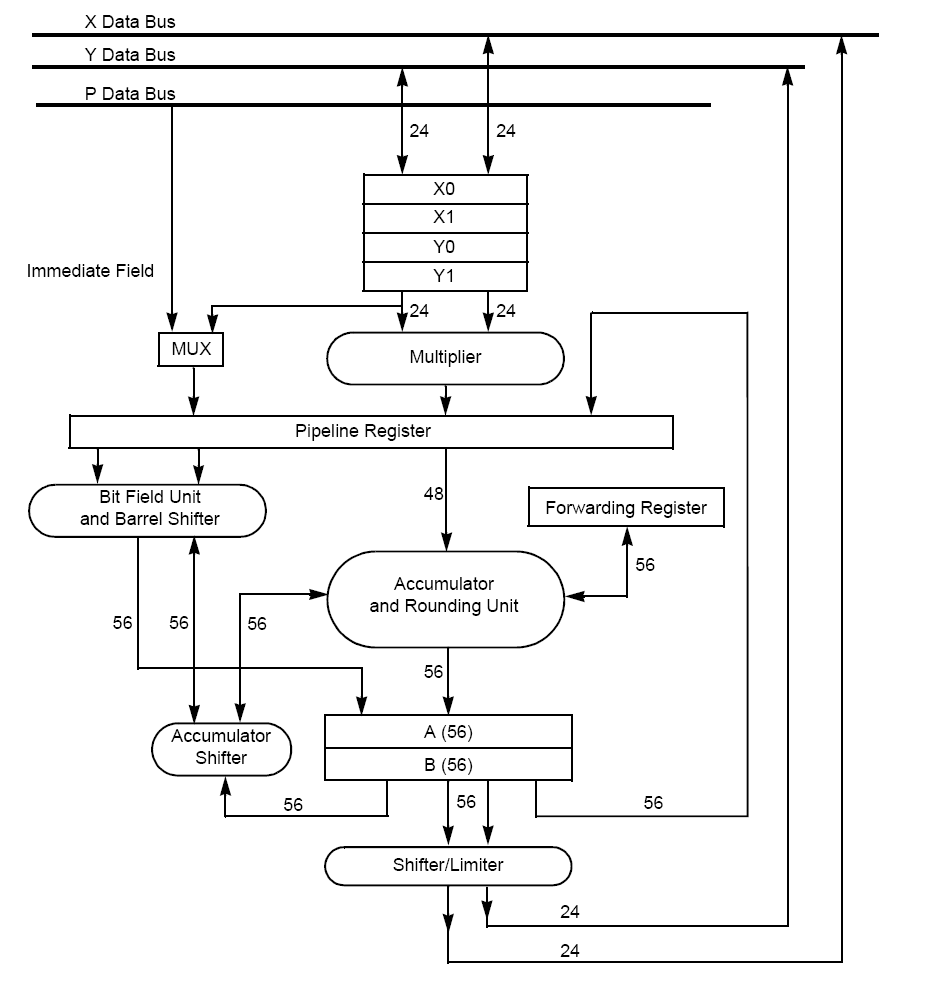

Jednostka arytmetyczno-logiczna (ALU) występuje w tej samej postaci we wszystkich procesorach rodziny DSP56300. Jej strukturę przedstawiono na rysunku 5.2. Jednostka ta składa się z następujących elementów:

układ mnożący,

układ akumulujący,

układy przesuwające, w tym układ typu barrel-shifter,

cztery 24-bitowe rejestry źródłowe X0, X1, Y0, Y1,

dwa 56-bitowe rejestry akumulatorów A i B,

rejestr pośredni, służący do realizacji potoku.

ALU wykonuje operacje wyłącznie na rejestrach (a nie na komórkach pamięci) i wynik operacji jest również zapisywany do rejestrów. Jest to cecha charakterystyczna architektury typu RISC. Operacje arytmetyczne i logiczne wykonywane są w 2-etapowym potoku. Wiąże się z tym problem przestoju potoku: jeżeli dany rozkaz odczytuje rejestr zapisywany przez rozkaz poprzedni, musi zostać poświęcony dodatkowy cykl zegara na dokończenie poprzedniego rozkazu.

Rys. 5.2. Schemat blokowy ALU procesorów rodziny DSP56300

Stosowana jest tutaj arytmetyka stałoprzecinkowa. Argumentami operacji arytmetycznych i logicznych mogą być:

24-bitowe dane z rejestrów X0, X1, Y0, Y1,

48-bitowe dane z połączonych parami rejestrów X1-X0 i Y1-Y0,

56-bitowe akumulatory A i B.

Podstawową funkcją ALU z punktu widzenia przetwarzania sygnałów jest mnożenie z akumulacją. Procesory rodziny DSP56300 mają możliwość mnożenia dwóch liczb 24-bitowych i akumulacji wyniku w 56-bitowym rejestrze. Mikroprocesor ma również specjalną instrukcję DMAC, która wykonuje mnożenie z akumulacją z 24-bitowym przesunięciem, co umożliwia wykonanie mnożenia liczb 48-bitowych w czterech cyklach.

Jednostka arytmetyczno-logiczna zapewnia także dodatkowe możliwości. Jedną z nich jest tryb nasycenia. W tym trybie liczba, która przekracza zakres możliwy do zapisania w rejestrze, będzie zastąpiona największą możliwą liczbą z odpowiednim znakiem. Poza tym istnieje możliwość zaokrąglania zawartości akumulatora do 24 bitów. Kolejną funkcją jest skalowanie operandów przez przesunięcie o 1 bit w lewo lub w prawo, co jest wykonywane razem z operacją arytmetyczną, bez poświęcenia dodatkowego cyklu zegara. ALU może również pracować w trybie 16-bitowym.

Pamięć wewnętrzna i port rozszerzenia pamięci

Jak pokazuje rysunek, procesor wyposażony jest w trzy bloki wewnętrznej pamięci, oznaczone X, Y i P. Dostęp do każdego z tych bloków odbywa się przy użyciu oddzielnej magistrali, co umożliwia korzystanie z nich jednocześnie. Pamięć P służy do przechowywania programu. Składa się ona z:

3 kilosłów 24-bitowych pamięci RAM przeznaczonej do przechowywania programu użytkownika,

30 kilosłów pamięci ROM z zawartością dostarczoną producentowi przez użytkownika,

192 słowa pamięci ROM z procedurami startowymi (tzw. bootstrap).

Procedury bootstrap zawarte w pamięci ROM pozwalają na załadowanie programu do pamięci RAM procesora po jego uruchomieniu. W celu umożliwienia łatwego pobrania programu z dowolnego źródła dostępnych jest wiele trybów wykorzystujących różne interfejsy procesora.

Pamięci X i Y są przeznaczone do przechowywania danych (np. próbki sygnału, współczynniki filtru). Każda z tych pamięci składa się z dwóch części:

5,5 kilosłów pamięci RAM,

6 kilosłów pamięci ROM.

W przypadku zastosowań, dla których pamięć wewnętrzna mikroprocesora okazuje się niewystarczająca, użytkownik ma możliwość dołączenia dodatkowej pamięci przez port rozszerzenia pamięci. Port ten ma 18-bitową szynę adresową, 24-bitową szynę danych oraz 11 linii sterujących.

Wśród linii sterujących występują 4 linie AA0..AA3, które mogą być zaprogramowane tak, aby uaktywniały się podczas dostępu pod określony przedział adresów i do określonego typu pamięci (P, X lub Y), jako sygnały Chip Select. Inną możliwością, jaką dają linie AA0..AA3 jest wykorzystanie ich jako dodatkowe linie szyny adresowej. Można wówczas uzyskać 22-bitową szynę adresową, co pozwala na zaadresowanie do 4 megasłów pamięci.

Port ten może być również skonfigurowany w taki sposób, aby obsługiwał pamięć DRAM (wtedy odpowiednie linie służą jako sygnały RAS i CAS). W tym trybie procesor automatycznie odświeża pamięć.

Układ generowania adresów

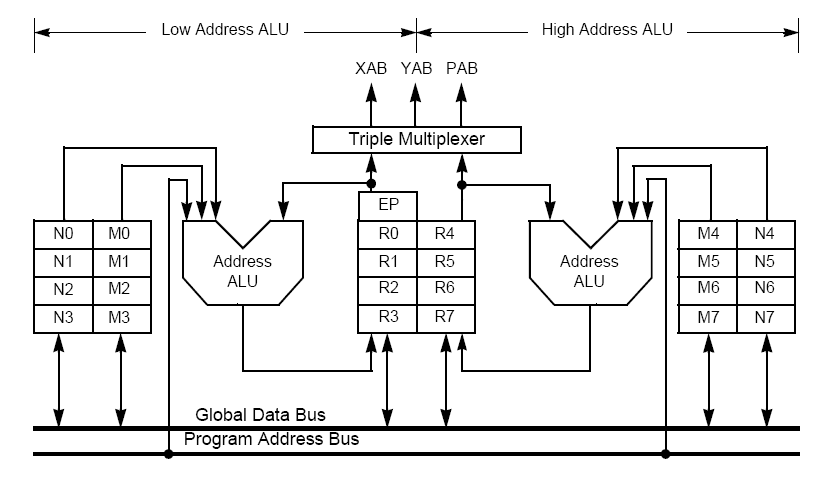

Rys. 5.3. Schemat blokowy układu generowania adresów procesorów rodziny DSP56300

Procesory rodziny DSP56300 charakteryzują się bogatym zestawem trybów adresowania. Za ich realizację sprzętową odpowiada układ generowania adresów (AGU). Budowę tego układu ilustruje rysunek 5.3. Jak widać, AGU składa się z dwóch jednakowych podukładów, co umożliwia jednoczesne adresowanie pamięci X i Y. Każdy podukład zawiera cztery zestawy po trzy rejestry oraz specjalną jednostkę arytmetyczno-logiczną zbudowaną z trzech układów dodających. Wyjścia obydwu podukładów wchodzą na multiplekser, skąd idą na szyny adresowe magistral X, Y i P.

Dzięki tak rozbudowanemu układowi AGU procesor obsługuje następujące tryby adresowania pośredniego rejestrami Ri:

bez zmiany rejestru Ri,

z postinkrementacją o 1,

z postdekrementacją o 1,

z predekrementacją o 1,

z postinkrementacją o wartość z rejestru Ni,

z postdekrementacją o wartość z rejestru Ni,

z przesunięciem o wartość z rejestru Ni, bez zmiany Ri,

z przesunięciem o wartość podaną bezpośrednio.

Wszystkie wyżej wymienione tryby mogą być wykonywane w arytmetyce liniowej, modulo Mi+1 albo z odwrotną propagacją przeniesienia (ang. reverse carry). Pozostałe tryby nie wykorzystują ALU adresowego. Są to tryby:

rejestrowy,

bezpośredni długi,

bezpośredni krótki,

bezpośredni wejścia/wyjścia,

bezpośredni krótki skoku,

natychmiastowy,

domyślny (ang. implicit),

licznikiem programu (PC) z przesunięciem o wartość w rejestrze Ri,

licznikiem programu (PC) z przesunięciem o wartość podaną bezpośrednio.

Układ DMA

Układ DMA umożliwia przesyłanie danych bez udziału jednostki centralnej, która może w tym czasie wykonywać inne czynności. Źródłem i celem transferu DMA może być pamięć wewnętrzna, pamięć zewnętrzna lub układy peryferyjne mikroprocesora.

Układ DMA w procesorach rodziny DSP56300 zawiera 6 niezależnie działających kanałów DMA. Obsługują one przesłania pod stały adres i przesłania z modyfikacją adresu, które dzielą się na tzw. przesłania jedno-, dwu- i trójwymiarowe. Pozwala to na realizację buforów cyklicznych, przesyłanie danych obrazu i obsługę innych często spotykanych struktur danych. Istnieje możliwość generowania przerwania po zakończeniu przesyłania bloku danych. Każdy kanał DMA może być wyzwalany przez sygnały z układów peryferyjnych bądź przerwania.

Interfejs równoległy Host Port

W celu umożliwienia sprawnej komunikacji z innym mikroprocesorem, wyposażono układ DSP56362 w 8-bitowy interfejs równoległy Host Port. Port ten może być skonfigurowany tak, aby miał 8-bitową szynę danych i 3-bitową szynę adresową lub też może pracować w trybie z multipleksowaną szyną danych i adresów, co rozszerza szynę adresową do 11 bitów, przy czym wielkość szyny danych nie ulega zmianie. Port może działać na słowach 8-, 16- i 24-bitowych.

Działanie linii sterujących Host Portu nie jest ustalone na stałe, lecz użytkownik ma możliwość wybrania kilku trybów. Tryby te są tak dobrane, że możliwe jest podłączenie większości popularnych procesorów bez dodatkowej logiki, tak aby Host Port widziany był przez procesor zewnętrzny jako pamięć. Wówczas DSP56362 pełni funkcję slave’a. Jednak w celu umożliwienia inicjalizacji transferu przez procesor sygnałowy, zastosowana została specjalna linia HOREQ, którą można połączyć z linią wywołania przerwania w procesorze zewnętrznym.

Interfejs szeregowy SHI

Port SHI umożliwia szeregową transmisję synchroniczną pomiędzy DSP a innym procesorem. Port ten obsługuje dwa znane protokoły: SPI Motoroli i I2C Philipsa. W przypadku każdego z nich DSP może stanowić mastera (w systemie z jednym masterem) lub slave’a. Transfer przez ten port może odbywać się słowami 8-, 16- lub 24-bitowymi. Podczas pracy jako SPI przesyłanie danych może odbywać się w trybie full duplex, tzn. dane mogą być jednocześnie nadawane i odbierane przez procesor sygnałowy.

Interfejs szeregowy ESAI

Port ESAI jest synchronicznym interfejsem szeregowym przeznaczonym do transmisji danych dźwięku. Może on pracować w trybie full duplex. Występuje tu 6 niezależnych nadajników i 4 odbiorniki. Jednocześnie można wykorzystać do 6 nadajników i odbiorników w sumie. Wszystkie nadajniki taktowane są wspólnym sygnałem zegarowym i analogicznie wszystkie odbiorniki, ale zegar nadajników jest niezależny od zegara odbiorników.

Port ESAI może zostać skonfigurowany do pracy w trzech trybach:

tryb podstawowy,

tryb sieciowy,

tryb transferu na żądanie.

W trybie podstawowym przesyłanie jest okresowe, przy czym w ciągu jednego okresu przesyłane jest jedno słowo. Ten tryb jest przydatny do komunikacji z przetwornikiem analogowo-cyfrowym lub cyfrowo-analogowym. W trybie sieciowym transmisja jest również okresowa, ale w ciągu okresu może być przesłane do 32 słów w kolejnych szczelinach czasowych. Zatem jest to multipleksacja z podziałem czasowym. W trybie na żądanie dane nie są przesyłane w stałych odstępach czasu, ale transfer rozpoczyna się, gdy zajdzie taka potrzeba. W tym trybie możliwe jest zrealizowanie protokołu SPI.

Interfejs szeregowy DAX

Interfejs DAX umożliwia procesorowi wysyłanie danych dźwiękowych zgodnie ze standardami S/PDIF i AES/EBU. Obok danych dźwiękowych mogą być również przesyłane inne dane. Dane przesyłane są w ramkach. Interfejs może pracować w trybie master (DSP generuje sygnał taktujący) lub slave (DSP odbiera sygnał taktujący z zewnątrz).

5.2.10. Blok czasomierzy

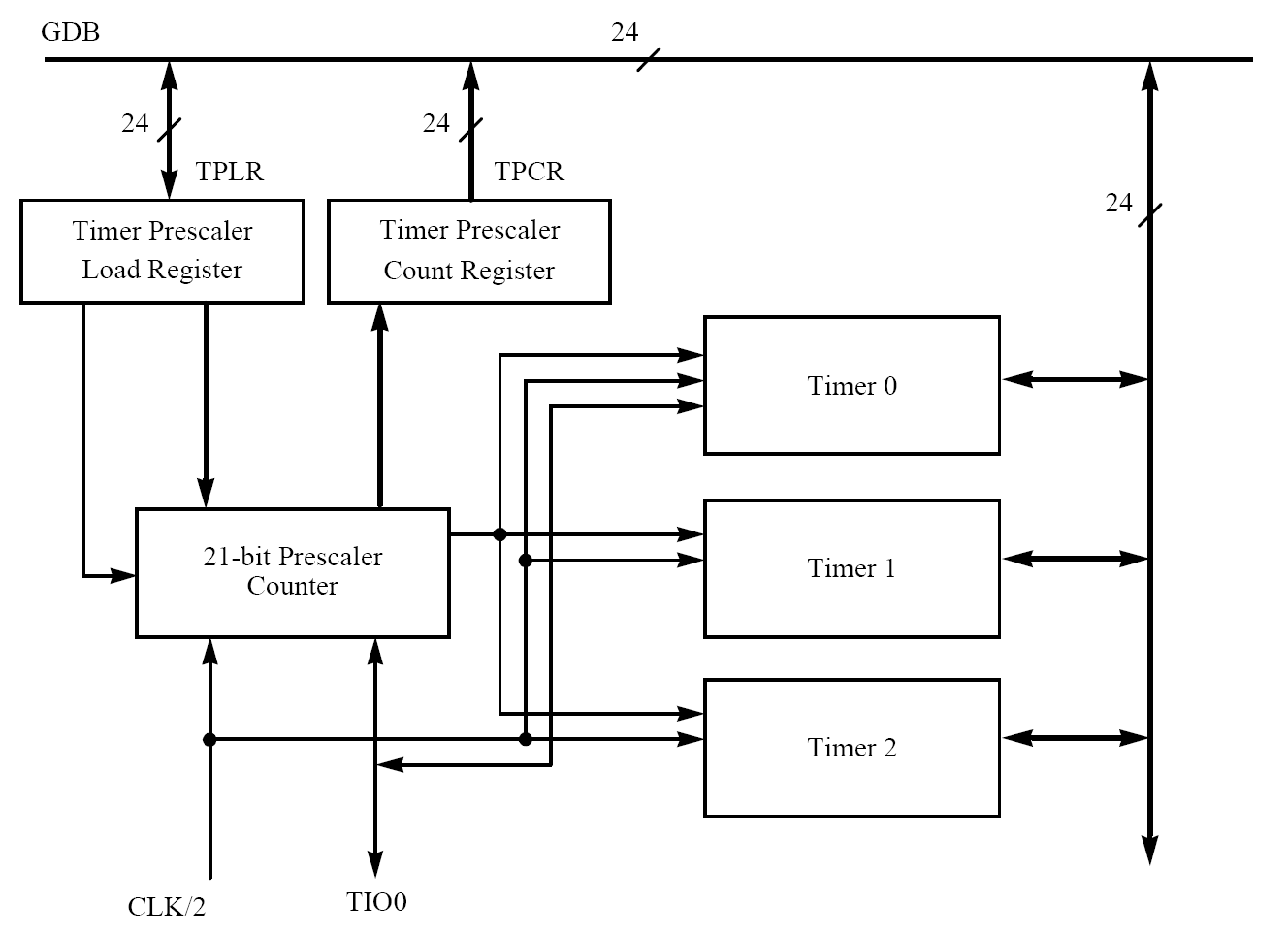

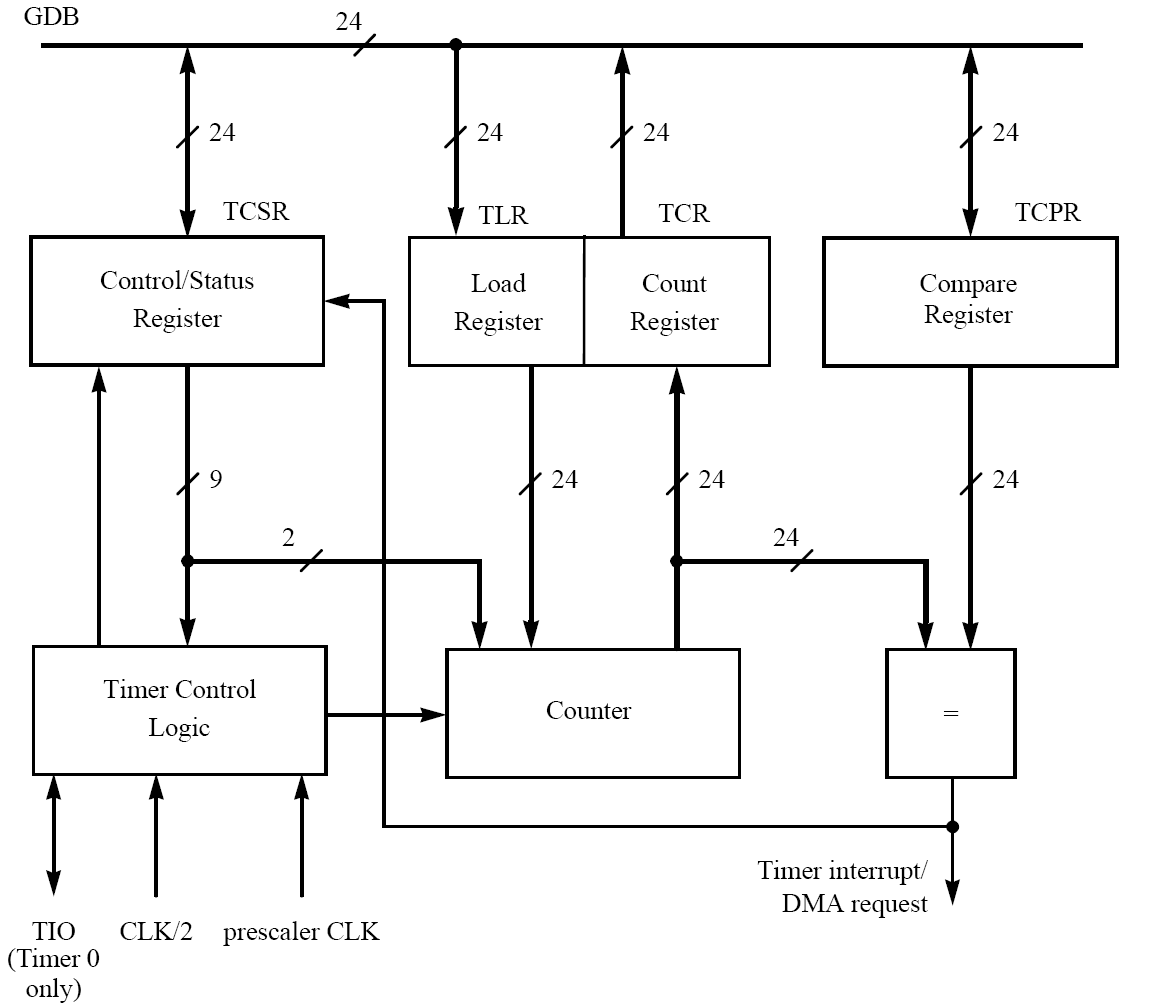

Mikroprocesor DSP56362 wyposażony jest w zestaw trzech identycznych układów mogących pełnić funkcję liczników lub czasomierzy, ponumerowanych od 0 do 2. Czasomierz 0 jest dostępny z zewnątrz procesora poprzez dwukierunkowe wyprowadzenie TIO0, natomiast czasomierze 1 i 2 są niedostępne z zewnątrz. Strukturę bloku czasomierzy przedstawia rysunek 5.4, a strukturę pojedynczego czasomierza – rysunek 5.5.

Rys. 5.4. Schemat blokowy zestawu liczników/czasomierzy procesora DSP56362

Jak widać, wejściem każdego z czasomierzy może być sygnał o częstotliwości dwa razy niższej od sygnału taktowania procesora podany bezpośrednio lub przez programowalny dzielnik częstotliwości (preskaler). W przypadku czasomierza 0 może to być dodatkowo sygnał z końcówki TIO0. Końcówka ta może również pełnić rolę wyjścia czasomierza 0, gdy nie jest wykorzystywana jako wejście.

Czasomierze mają możliwość pracy w wielu trybach różniących się sposobem reakcji na sygnały wejściowe jak i zachowaniem sygnału wyjściowego. Dzięki temu możliwe jest zrealizowanie wielu przydatnych funkcji bez obciążania jednostki centralnej. Są to następujące funkcje:

Rys. 5.5. Schemat blokowy pojedynczego układu licznika/czasomierza procesora DSP56362

g enerowanie przerwania powtarzanego co określoną liczbę cykli wewnętrznego zegara,generowanie impulsów na końcówce TIO0 powtarzanych co określoną liczbę cykli wewnętrznego zegara,

cykliczne zmiany sygnału na końcówce TIO0 powtarzane co określoną liczbę cykli wewnętrznego zegara,

generowanie przerwania powtarzanego co określoną liczbę cykli sygnału doprowadzonego do końcówki TIO0,

pomiar szerokości impulsów na końcówce TIO0,

pomiar okresu sygnału na końcówce TIO0,

pomiar czasu od chwili uruchomienia czasomierza do wystąpienia się sygnału na końcówce TIO0,

modulacja szerokości impulsów na końcówce TIO0,

tryb watchdog z generowaniem impulsów bądź cykliczną zmianą stanu końcówki TIO0.

komentarze

Copyright © 2008-2010 EPrace oraz autorzy prac.